Silicom’s gateway applications acceleration with DYNANIC

Silicom, in collaboration with DYNANIC, presents a SmartNIC specifically designed and tailored to support the acceleration of several gateway applications, especially those focused on cybersecurity.

This FPGA-powered solution enables packet capture and pre-processing at speeds up to 400 Gbps, making it ideal for demanding environments such as data centers and telecommunications infrastructure. It supports a wide range of network protocols and enables traffic distribution to CPU cores via hundreds of independent DMA channels based on user-defined rules.

This solution supports real-time feature extraction for precise network monitoring and effective detection of anomalies or threats. Beyond standard metadata such as IP addresses, packet lengths, and timestamps, it can compute advanced metrics like entropy and perform deep packet inspection with pattern matching.

It also provides hardware-level DDoS mitigation, with the ability to filter hundreds of thousands of flows, IP prefixes, and custom rule sets. Configuration is handled through easy-to-use, standardized interfaces such as DPDK RTE Flow. No hardware development tools or FPGA expertise are required—DYNANIC delivers all necessary customizations through its pre-built and configurable modules, enabling software developers to fully leverage the potential of FPGA acceleration.

Whether used for traffic filtering, intrusion detection, lawful intercept, or AI-based network monitoring, this SmartNIC offers a powerful and accessible platform that combines high performance with operational flexibility.

- The Solution

- Block Diagram

- Compatible with

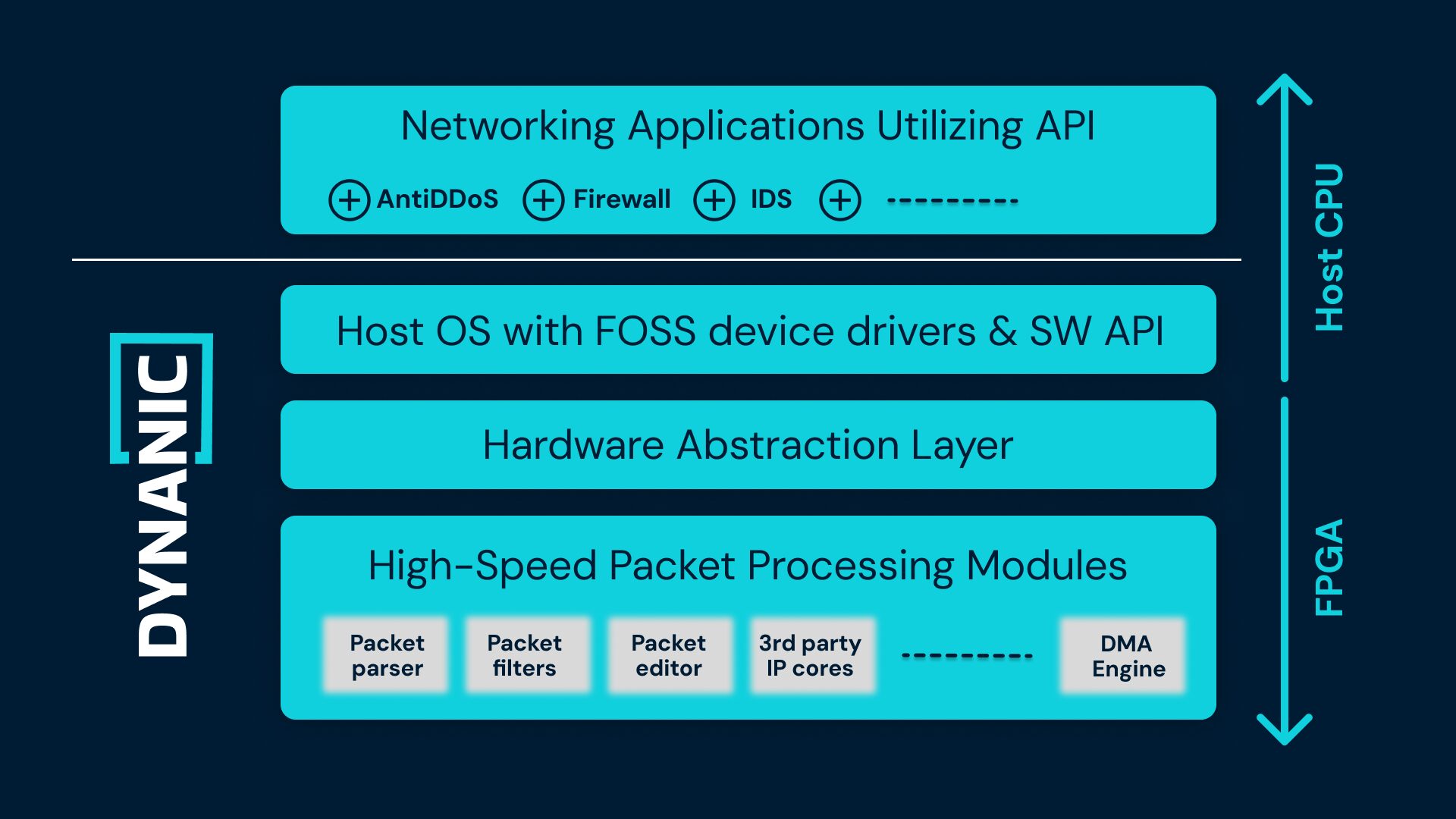

At the core of the solution lies a highly optimized and configurable FPGA-based packet processing pipeline, purpose-built for high-throughput network monitoring and security systems. This pipeline integrates three essential components: a configurable packet parser for extracting selected metadata from L2 to L4 packet headers, flexible flow-based filtering engines for filtering and matching, and an ultra-fast DMA subsystem that transfers network packets to host memory while efficiently distributing traffic across multiple CPU cores.

The architecture also supports optional pattern matching, allowing selected sets of strings to be searched within packets as part of specific filtering rules. This enables advanced use cases such as intrusion detection and application-aware filtering. Moreover, it also supports the 3rd party FPGA IP cores to provide another level of flexibility. So that cryptographic, compression on other functionality can be provided based on specific needs.

To achieve optimal performance with minimal FPGA resource usage, the solution leverages DYNANIC’s proprietary multi-bus technology. Multiple packets are processed in parallel within a single pipeline stage, increasing throughput while keeping the logic footprint low. This architecture is designed for scalability, supporting current 400 Gbps deployments and being future-proofed for 800 Gbps and beyond.

Key Features

- No need for FPGA development; the processing pipeline is provided

- Standardized and open-source DPDK software stack

- Pipeline fully controlled through the standard RTE Flow interface

- Full throughput to and from host RAM (depending on PCIe bandwidth)

- Configurable packet parser supporting protocols from L2 to L4

- Multiple filtering options using internal or external memory

- Flow tracking with fast atomic insertions and removals from the host

- Compatible with various link speeds, even on the same card

- Lossless traffic processing at wire-speed up to 400 Gbps

- 3rd party FPGA IP cores integration possible

Standard Filtering Capacity by Card

Card | Exact Match | Longest Prefix Match | CAM |

FB2CDG1@AGM39D-20XP2 (Thunderfjord) | 2.5M | 1.4M | 15k |

FB2CG1@AGF14-A0S2 (N6010) | 961k | 574k | 6k |

FB2CG@KU15P-2 (Savona) | 489k | 278k | 3k |

FB2CGHH@KU15P-2 (Tivoli) | 489k | 278k | 3k |

Note: The number of supported filtering rules can be adjusted based on the requirements of the target application.

Card and FPGA Requirements

The solution is designed for broad compatibility across a wide range of Silicom’s FPGA-based network interface cards. Thanks to its hardware abstraction layer, it operates independently of the underlying FPGA chip vendor, supporting both Intel (Altera) and AMD (Xilinx) Silicom’s cards, which ensures maximum flexibility when selecting hardware for specific deployment scenarios.

The solution is optimized for high-speed network interfaces, starting from 100GE and scaling up to 400GE. Traffic at 400 Gbps can be handled within a single, high-throughput pipeline, while multiple parallel pipelines can be instantiated to accommodate even more complex workloads or to take advantage of multi-port cards and bigger FPGA devices.

To support demanding applications such as large-scale flow tracking or extended filtering capacity, the solution can be configured to utilize external memory resources. These resources are provisioned based on user requirements and tailored to the capabilities of the selected card.

For a complete list of supported hardware platforms, refer to the Compatible with tab.

Solution Package

The solution is delivered as a complete package, including both FPGA firmware and a host-side software stack.

FPGA Card

The package includes a verified and production-ready FPGA bitstream designed for the selected Silicom card. This allows for immediate deployment without the need for hardware development. In addition, the packet processing pipeline can be tailored to specific use cases through custom modifications provided by DYNANIC or even with 3rd party FPGA IP cores provided, ensuring maximum adaptability to application requirements.

Host Software

- Open-source software stack with:

- Linux drivers and utilities for configuration, monitoring, and testing

- DPDK-based API implementation using RTE Flow

- Compatible with RHEL 8 and derivatives (Rocky, Oracle, etc.); Debian-based distributions available on request

All components are bundled in a single package, complete with full documentation.

Documentation

The solution comes with a detailed Quick Start Guide that walks users through setup and integration. It includes practical software examples to help developers accelerate application development and take full advantage of the complete solution.

Free Trial for Testing

A free trial version of the solution is available for download. The trial is time-limited, but there are no restrictions on throughput, allowing users to test the performance and integration under realistic conditions. For switching to the production version, only a valid license key is needed.