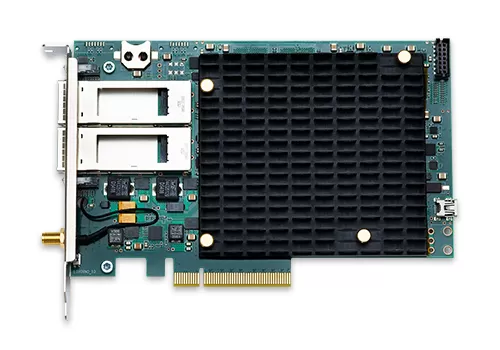

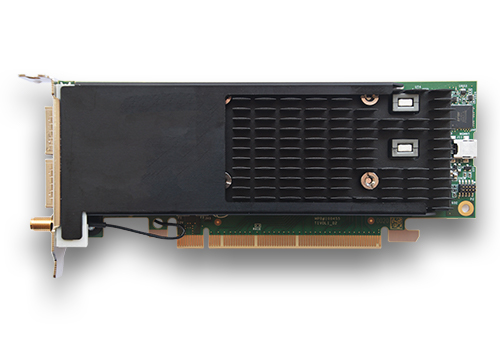

Silicom’s BlueFjord FPGA SmartNIC

The Silicom BlueFjord FPGA SmartNIC (FBAP4@AGF series) is a high-performance OEM hardware acceleration platform designed for compute-intensive workloads in server environments, including cryptographic processing, compression, and 5G RAN FEC/LDPC.

Built on the Altera® Agilex™ 7 F-Series FPGA with a dual F-tile package, BlueFjord supports configurations featuring a Hard Processor System with four 64-bit ARM Cortex-A53 cores alongside a powerful programmable logic fabric. FPGA capacity ranges from 573K to 2,692K logic elements, enabling tailored solutions that meet a broad spectrum of application requirements.

Serving as the hardware foundation for Silicom’s Accelerated Crypto Adapter (SACA) solution, BlueFjord offers a scalable and versatile platform capable of offloading diverse crypto algorithms. Crucially, support for Elliptic Curve Cryptography (ECC) and Post Quantum Crypto acceleration (PQC) available, supporting OpenSSL 3.5. Its compact form factor and low power consumption make it an ideal choice for solutions such as the Eideticom® NoLoad. NoLoad leverages BlueFjord to offload demanding crypto/data processing tasks from the host CPU, enhanced by onboard processor cores, extending feature capabilities of the card.

BlueFjord also serves as the primary platform for Silicom’s Accelerated RAN Adapter (SARA), engineered to meet the latest 5G New Radio standards by offloading FEC/LDPC and HARQ operations in 5G mobile radio access networks, significantly reducing deployment footprint while ensuring peak performance and compatibility.

Beyond its Silicom offered applications in SACA, SARA, and Eideticom® NoLoad, Silicom provides a comprehensive board support package including development tools, drivers, and software to facilitate rapid FPGA offload design and board management, empowering customers to implement custom acceleration solutions. Each BlueFjord SmartNIC undergoes rigorous validation to guarantee reliability and scalability in large-scale deployments requiring FPGA acceleration, making it a robust and flexible platform for next-generation compute-intensive workloads.

Target Applications

- Compute offloading

- Crypto look-aside offloading

- Post Quantum Crypto accelration

- Symmetric and asymmetric crypto

- Signature generation and verification

- Bulk encryption/decryption

- Compression offloading

- 5G FEC/LDPC offloading