Disaggregated and virtualized Radio Access Network (RAN) enables 5G market competition and customer choice with lower equipment costs, and improved network performance. Open RAN deployments can be implemented in vendor-neutral hardware and software-defined technology, based on open interfaces and community-developed standards.

Scalability and precise time synchronization has become the key requirements for Network Interface Cards(NIC) targeting 5G networks in Distributed Unit (DU), Centralized Unit (CU) and Centralized Cloud.

Our FPGA SmartNICs leveraging on open source software stacks such as the popular Linux precision time protocol (ptp4l) and Data Plane Development Kit (DPDK) interfacing with open source FPGA Shells such as the OpenNIC or Open FPGA Stack(OFS), all running on hardware platforms with state-of-the-art TimeSync architecture designed to meet the strict 5G timing requirements.

In the previous blog post we presented how you can extend grand master (T-GM) functionality across multiple TimeSync FPGA Smart NIC cards , while in this article we will show how you can deploy our SmartNIC in virtualized environments utilizing the single root I/O virtualization (SR-IOV) interfaces with our OpenNIC linux drivers and DPDK software.

Scalability with precision: PTP4L, OpenNIC, DPDK, and SR-IOV Unleashed

>OpenNIC: Redefining Network Flexibility

OpenNic facilitate rapid prototyping of hardware-accelerated network-attached applications. It offers an FPGA-based NIC platform designed for the open source community with well-defined data and control interfaces and is designed to enable easy integration of user logic. It consists of multiple components: a NIC shell, a Linux kernel driver, and a DPDK poll mode driver.

>DPDK: Accelerating Data Plane Performance

>DPDK: Accelerating Data Plane Performance

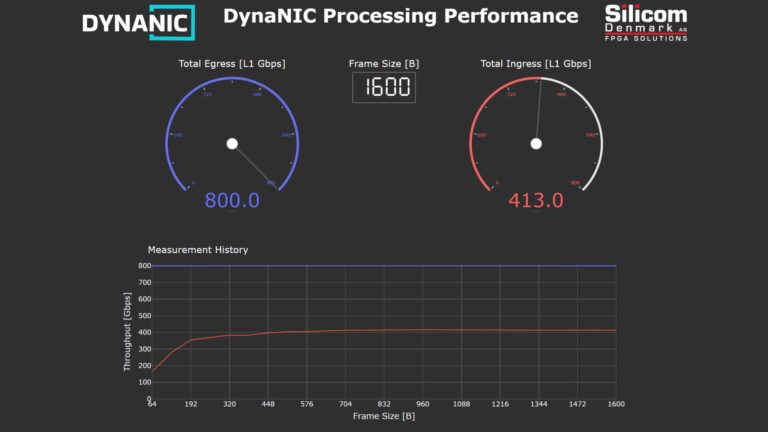

Enter DPDK, the linchpin for accelerating data plane performance. With its high-throughput processing capabilities, DPDK ensures that our FPGA card becomes a powerhouse for handling data-intensive tasks. The marriage of OpenNic and DPDK results in a symbiotic relationship, where flexibility meets high-speed data processing, a combination poised to redefine the standards of network applications.

>SR-IOV: Virtualization with Precision

SR-IOV takes virtualization to the next level by enabling the creation of multiple virtual functions with direct access to the FPGA card. This not only enhances scalability but also ensures precision in resource allocation. The result is a network architecture that thrives on efficiency, seamlessly distributing workloads across virtual functions.

Time synchronization in a secure way: The Embedded Processor System Advantage

One of the key differentiator in our TimeSync SmartNICs compared to traditional NICs is that the PTP stack is running on the card in the FPGA embedded ARM CPU. With this implementation the PTP packets are separated from the rest of the Ethernet stream sent to the HOST system. By this approach the load on the host side CPU will not influence by any mean the precision of the time synchronization, even if you deploy the card in a virtual environment with multiple Virtual Machines(VM) attached through the virtual functions(VF) of the SR-IOV interface.

From network security perspective, the isolation of the PTP stack on the card gives you extra options to deal against “time-spoof” , you can leave unencrypted the PTP packets and apply encryption only on your IP traffic towards the HOST network interface.

This strategic move optimizes the FPGA card‘s capabilities, ensuring that mission-critical tasks operate with the precision and reliability required in today’s dynamic networking landscape. Click below on “Read More About Our Solution” to see the full solution brief.

Frequently Asked Questions

Q: How does OpenNic contribute to scalable network applications?

OpenNic serves as the foundation, providing the necessary framework for scalable network applications. Its unique features enable seamless integration with DPDK and SR-IOV, enhancing overall performance.

Q: What sets DPDK apart in powering network performance?

DPDK stands out for its ability to accelerate packet processing, ensuring optimal performance for network applications. Its efficiency and speed make it a crucial component of our integrated solution.

Q: How does SR-IOV enhance virtualization in this context?

SR-IOV facilitates efficient virtualization by allowing multiple virtual machines to share a single FPGA card without compromising performance. This ensures a streamlined and high-performing network.

Q: What critical functions are offloaded to the embedded Processor System?

Critical functions, such as Precision Time Protocol (PTP), are offloaded to the embedded Processor System, optimizing the overall performance and reliability of the network.

Q: How does the integration of OpenNic, DPDK, and SR-IOV benefit small businesses?

The integration offers small businesses improved network performance and scalability at a cost-effective rate, providing them with a competitive edge in the market.